网站设计要求 优帮云/快速的网站设计制作

文章目录

- 结构语句

- initial

- always语句

- 赋值语句

- 阻塞赋值

- 非阻塞赋值

- 条件语句

- if _ else 语句

- case语句

结构语句

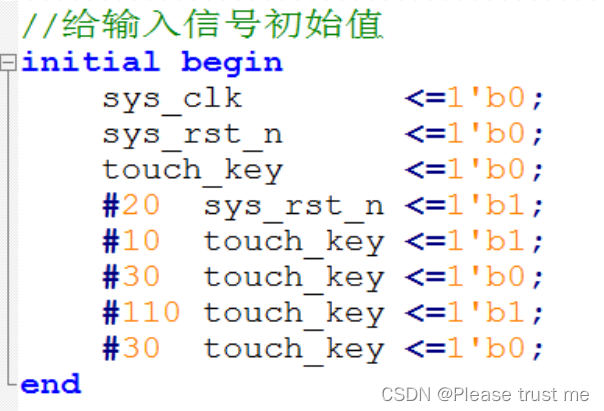

initial

initial语句它在模块中只执行一次,它常用于测试文件的编写,用来产生仿真测试信号(激励信号),或者用于对寄存器变量赋初值。

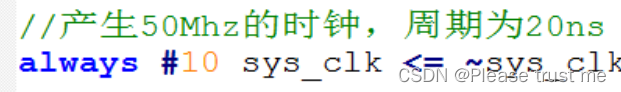

always语句

always语句一直在不断地重复活动。但是只有一定的时间控制结合在一起才有作用

always的时间控制可以是沿触发,也可以是电平触发;

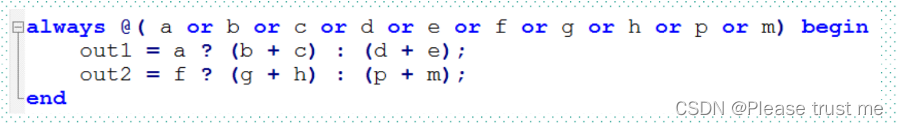

可以是单个信号,也可以是多个信号,多个信号中间要用关键字or连接

always语句后紧跟的过程块是否运行,要看它的触发条件是否满足。

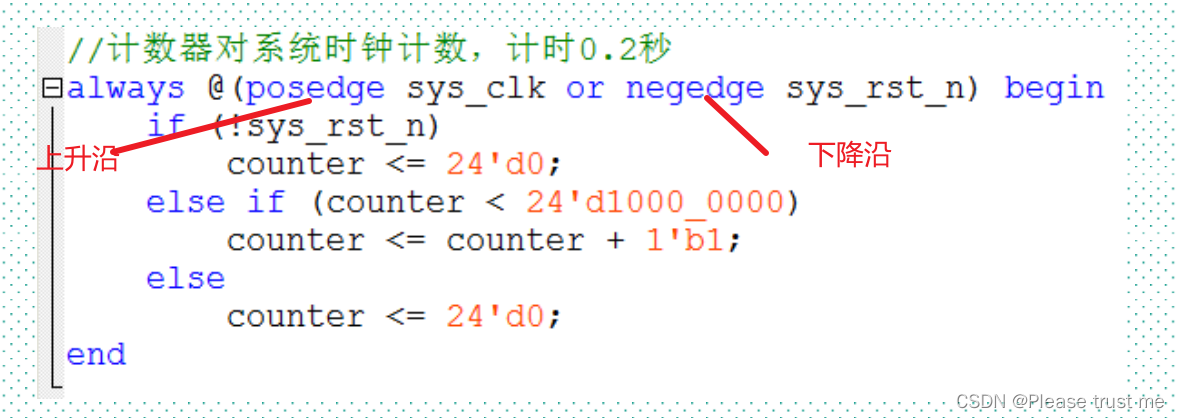

沿触发的always块常常描述时序逻辑行为。

由关键字or连接的多个事件名或信号名组成的列表称为“敏感列表”

电平触发的always块常常描述组合逻辑行为。

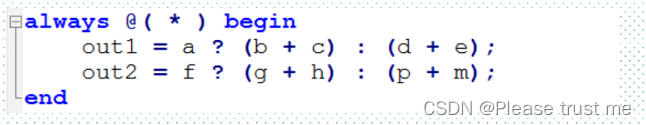

如果组合逻辑块语句的输入变量很多,那么编写敏感列表就会很烦琐且容易出错。

@(*)表示对后面语句块中所有输入变量的变化都是敏感的。

根据逻辑功能的不同特点,可以将数字电路分为两大类:

组合逻辑电路和时序逻辑电路。

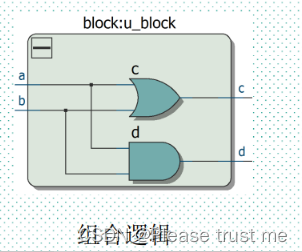

组合逻辑电路中,任意时刻的输出仅仅取决于该时刻的输入,与电路的状态无关。

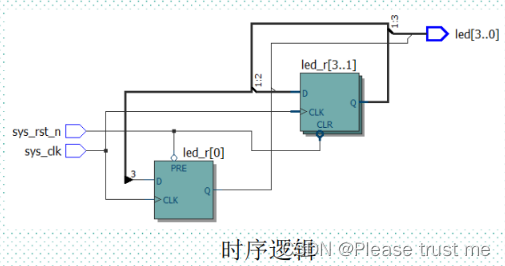

时序逻辑电路中,任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态。或者说还与以前的输入有关,因此时序逻辑必须具备记忆功能

赋值语句

Verilog HDL语句中,信号有两种赋值方式

- 阻塞赋值(blocking),如

b = a; - 非阻塞赋值(Non_Blocking) ,如

b <= a;

阻塞赋值

阻塞赋值可以认为只有一个步骤的操作:

即计算RHS并更新LHS。

所谓的阻塞赋值的概念是指,在同一个always块中,后面的赋值语句是在前面的语句结束之后才开始赋值的。

always @(posedge clk or negedge rst_n)beginif(!rst_n)begina=1;b=2;c=3;endelse begina=0;b=a;c=b;end

end

非阻塞赋值

非阻塞赋值的操作过程可以看作两个步骤:

- 赋值开始的时候,计算RHS;

- 赋值结束的时候,更新LHS。

所谓非阻塞的概念是指,在计算非阻塞的RHS以及更新LHS期间,允许其他的赋值语句同时计算RHS和更新LHS。

always @(posedge clk or negedeg rst_n)beginif(!rst_n)beigina <= 1;b <=2;c <=3;endelse begina <=0;b <=a;c <=b;end

end

非阻塞赋值只能用于对寄存器类型赋值,因此只能用在initial块和always块等过程中

在描述组合逻辑的always块中用阻塞赋值=,综合成组合逻辑的电路结构。

这种电路结构只与输入电平的变化有关系。

在描述时序逻辑的always块钟用非阻塞赋值 <=,综合成时序逻辑的电路结构;

这种电路结构往往与触发沿有关系,只有在触发沿时才能发生赋值的变化。

注意:在同一个always块种不要即用非阻塞赋值又用阻塞赋值

不允许在多个always块中对同一个变量进行赋值

条件语句

if _ else 语句

格式1

if(a > b)out = data_1;

格式2

if(a>b)out = data_1;

else out = data_2;

格式3

if(表达式1)语句1;

else if(表达式2)语句2;

else if(表达式3)语句3;

else语句4;

条件语句必须在过程块中使用。

过程块语句是指由inital和always语句引导的块语句。

使用方法

- 允许一定形式的简写

if(a)等同于 if(a==1)

if(!a)等同于if(a!=1) - if语句对表达式的值进行判断,若为0,x,z按假处理;若为1,按真处理。

- if和else后面的操作可以用begin和end包含多个语句。

- 允许if语句的嵌套

if(a)beigin语句1;语句2;

end

else begin语句3;if(!b)语句4;else语句5;

end

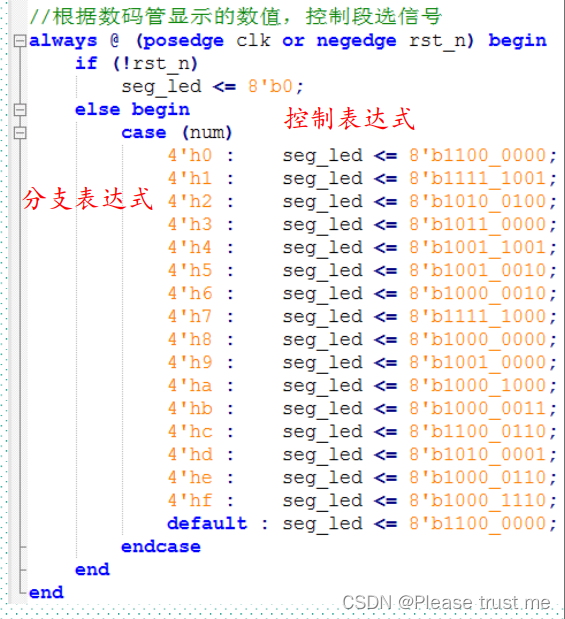

case语句

多分支选择语句

- 分支表达式的值互不相同;

- 所有表达式的位宽必须相等;不能用’bx代替n’bx

- casez 比较时,不考虑表达式中的最高阻值

- casex 不考虑高阻值z和不定值x